Zen 微架构探究——后端(Back-End)

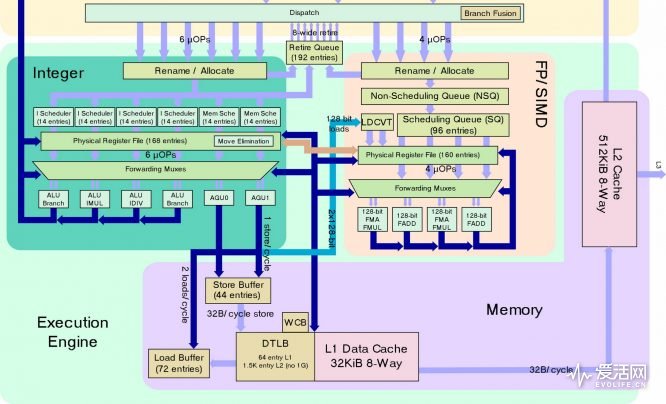

处理器的后端包括了调度与执行、载入/存储等模块,和英特尔的设计不同,Zen 或者说 AMD 自 K7 以来处理器的整数和浮点执行资源是分离式的,有各自独立的调度器和执行流水线。

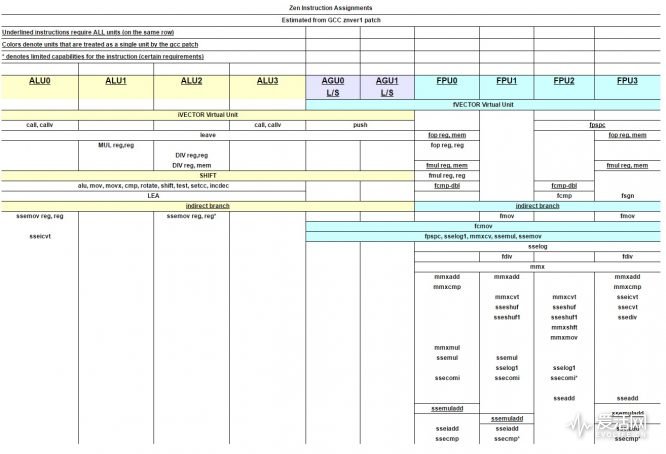

下图所示是根据 AMD 提交的 GCC 补丁信息而推测的 Zen 各个执行端口指令执行能力图:

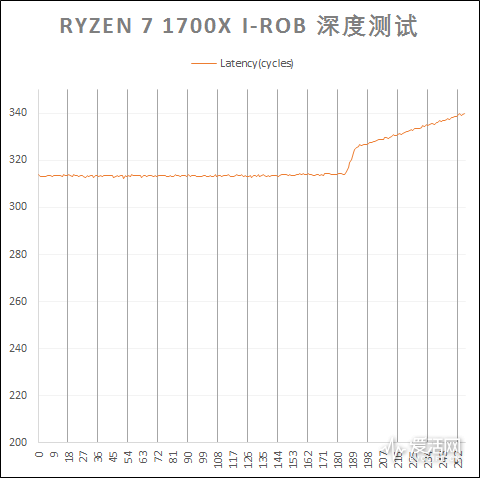

现在的乱序执行处理器会在解码器和执行单元之间设置一个重排序缓存(ROB),可以让指令乱序执行,然后依照程序原有的顺序递交计算结果,在写结果的时候,指令的结果会暂时存放在 ROB 里,之后指令执行的结果再被存储到寄存器或者系统内存中,如果其他指令急切需要该结果,那么 ROB 就可以直接为其传输所需的数据。

我们对 Zen 和 KabyLake 的 ROB 进行了测试:

从测试结果来看,Intel KabyLake 的 ROB 时延要比 Zen 快差不多 100 个周期,而在容量上两者的测试结果符合官方的资料(Zen:180 条目,KabyLake:224 条目)。

整数单元

其中整数执行具有一个 168 条目的物理寄存器堆,可以提供给 4 个算术逻辑单元及两个地址生成单元使用(例如重命名),这样可以让 Zen 的内核每个周期进行 6 个微操作的发射调度,每个整数执行端口具有自己的 14 个条目的调度深度。作为对比,Intel 的 KabyLake 整数物理寄存器堆大小是 180 个。

四个算术逻辑单元中只有两个可以跑分支指令,另两个中的一个可以跑 IMUL(带符号乘法)操作、一个指令能跑 CRC 操作,不过 4 个整数执行流水线的具体差别需要待 AMD 的优化指南或者类似资料出来后才能确定。

Zen 还包含了可以用来追踪分支指令的差分检查点以及传输消除和冗余值消除等增强特性。

浮点单元

Zen 的浮点单元可以每个周期从分发单元获得 4 个微操作,拥有 160 个物理浮点寄存器堆(英特尔的 Skylake/KabyLake 的向量寄存器堆有 168 个)。

在浮点微操作抵达调度队列之前,会先抵达 Non-Scheduling Queue(NSQ),这个 NSQ 是一个等待缓存。这是因为浮点指令通常需要较长的时延,因此在分发单元的时候就会有一堆待命的微操作。NSQ 会尝试透过浮点指令队列化来减少这些排队,从而让分发器可以保持类似提供给整数流水线的分发水平。

此外,NSQ 还能提前对浮点指令内存组元进行处理,使其在抵达调度器队列的时候就已经就绪。

Zen 的浮点引擎有一条单独的流水线进行 128 位载入操作。

浮点调度器有 4 流水线(比 Excavator 多一条),都可以支持 128 位浮点操作,AMD 对 Zen 的浮点流水线设计也是依照 128 位来优化的。

SSE 系列以及 AVX 1/2 都获得了 Zen 支持,其中的 256 位指令是拆开成两个 128 位操作一次执行,然后重新将其融合。这样的实现方式让 Zen 在类似操作上落后于英特尔,后者现在都有专门的 256 位处理电路。Zen 还支持 SHA、AES 指令,透过两个 AES 单元实现,用于改进加密性能。

内存子系统

载入/存储单元由两个可以同时执行 L/S 指令的 AGU 管理。Zen 具有和 KabyLake 一样大(72 条目)、支持乱序载入的载入队列,而在存储队列方面 Zen 拥有 44 个条目(KabyLake 是 56 条目)。

Zen 采用了分离式的 TLB 数据流水线设计,数据高速缓存被填充的时候可以访问 TLB 标签,确定数据是否可用然后发送其地址到 L2 高速缓存开始提前进行预取。

Zen 可以每周期进行两条 Load 操作(每条可以处理 2*16 字节)以及每周期一条 Store 操作(1*16 字节)。

L1 TLB 可以支持所有页面尺寸,深度为 64 条目,L2 TLB 缺乏 1GiB 页面支持,深度为 1536 条目。

Zen 拥有 4 路组相联 64KiB L1 指令高速缓存以及 8 路组相联 32KiB L1 数据高速缓存,两高速缓存都能够以 32 字节/周期的带宽从 L2 高速缓存获取指令或者数据。

Zen 每个内核有自己独立的 L2 高速缓存,大小是 512 KiB,采用 8 路组相联,具有统一化(不区分指令和数据)、包容化(里面存放有 L1 高速缓存的指令和数据)、代码私有化的设计。

Zen 的内核之间有一个共享的 L3 高速缓存,L2 高速缓存可以每周期 32 字节的带宽从 L3 高速缓存读取和写入(双向总线,各向各周期 32字节)。

同时多线程(SMT)

Zen 最大的改进就是引入了同时多线程(Simultaneous MultiThreading,SMT,也有人翻译作同步多线程)支持,该技术类似于 Intel 15 年前首次在 NetBurst 微架构体系的 Xeon 所引入的 Hyperthreading(原代号是 Jackson)技术。从技术角度而言,Zen 是一个正确的 SMT 处理器,各个内核均可以全程同时执行两个线程。

SMT 的目的是透过执行多线程实现资源的充分利用。

在单线程模式下,所有的资源都可以被该线程所使用,采用 SMT 后,Zen 的内核同时有两个线程,它会尝试为两个线程共享尽可能多的资源以平衡吞吐需求,并且按照软件的需求为每个线程提供适当的单元分配。

Zen 的各个单元可以根据执行的负荷动态地切换其资源。被两个线程竞争共享的资源(上图红色标记)包括有执行单元、调度器、寄存器堆、解码器、高速缓存(包括微操作高速缓存)。

以青色标记的载入队列、ITLB 以及 DTLB 等单元同样是竞争共享,但是需要 SMT 标记,也就是说,资源(例如队列深度)可以被两个线程共享,但是条目值(例如地址)只能被具有指定标记的线程访问。

以蓝色标记的分支预测器以及两个寄存器重命名/分配单元是以优先度算法来进行竞争共享的。Zen 提供了一个逻辑机制,可以让某个线程临时获得比其他线程优先度更高的资源分配。例如某个线程要对分支预测器进行清空,被赋予临时优先度的线程可以拾取到足够再次重新开始的指令数。此外,在分发器中也有类似的逻辑机制,可以确保两个线程具有高吞吐率以及执行单元的高使用率。

要发表评论,您必须先登录。

好精细的文章 。

1700X屏蔽成4C8T是屏蔽一组CCX吗?

贴吧过来围观神文,太牛逼了,1年前就精确推测到后面的8700和2990wx,作者是amd的把

1年后再看,确实是厉害,后面的发展也和这个文章写的差不多

broadwell是15级流水线?kabylake是17级流水线?对应惩罚周期来看,是这样吗?

牛逼,牛逼,牛逼,这文章太他妈牛逼了

关于1700默认电压是1.35之高,在BIOS中关闭 自动睿频的功能 就会变成在1.03附近,之前在官超软件里观察,在单核到达最高加速频率3.7的时候 才会到达1.35V的电压。软件中超频到3.7G 电压1.25 ,满载功耗在105W附近。网上许多在1.2V的电压下就可以稳定3.7,可是我这个1.2V在X264编码中 会黑屏

电压太低了,系统不稳定,要么加压要么降频。

1.25 3.7大众体质。

你把防掉压等级 提升到最高 你就可以 1.21V 超频到3.7了

爱憎分明,好似cho大还魂,gz风采依旧

最后的价格有问题,这价格是microcenter的价格,全美仅仅十几个或者二十几个店铺,绝大多数的美国人是不能够以这价格买到的,因为intel不给microcenter在网上卖。我建议还是以亚马逊或者新蛋的价格为准。(ps我才不会说两年前295买的5820k 上周以312价格卖走)

所以我们依然要选择I5/I7 。农企翻身,不存在的

服气

看了大炮村的i3秒1800x文章,说是抄这里的,一上午看完,只能膜拜大神

请问内存3000下的L3延迟是多少

RYZEN暂时无法再DDR4 3000 2CH下稳定工作。

PRO-A大神能不能提供个LLC延迟测试脚本?我们在设计的一款CPU也有LLC,想测试下

文中有个错误,SSE类指令集和AES指令集都是128bit,而AVX和AVX2都是256bit,64bit的是已经被淘汰的MMX。

SSE是32bit单精度,4d向量是128bit。

没听说过SSE是32bit单精度的说法。

SSE支持32bit、64bit浮点的向量操作,SSE2扩展了对8bit、16bit、32bit、64bit整数的向量操作,而SSE的XMM向量寄存器的宽度是128bit。

相对应的,AVX支持浮点的操作,AVX2扩展了对整数的操作。

请复习IEEE754

我从事这个行业这么多年,第一次听说SSE是128bit

居然认真地看完了……我是A粉么?!

技术兵力一个层级?小编你真敢吹!!!!

以前是父与子,现在是大哥与小弟,虽然还是不及,但至少是“同辈”了。

后藤那个图是不是有问题?看起来左上角那块更像MC,而标注MC的部分反而是IO

6666666666

基本参考wikichip翻译。。。

文章比cpu本身有趣多了,这是至今中文cpu评测最强无疑

要是能出四核心八线程版本对应i3的价格区间那还是不错的选择

核心数量太多并没有太大用处

前来膜拜神文

從超頻結果可見,GF仍然是AMD最大的拖後腿

要不要考慮去抱INTEL大腿,INTEL代工招商中,ZEN配INTEL 14NM還不屌炸天? XD

三星和台積電不知道有沒有機會代工了

回归神来这篇评论已经爆满了啊

小编,文中Ryzen 7 1700X模拟Ryzen 5的同频4GHz测试,是屏蔽一组CCX而来的吗?

周末再来读一次

跪拜。好文!

写的太棒了~!

编辑搜集了相当多的数据资料,整理论述的相当专业和详实,菜鸟膜拜!

特地为了点赞和评论注册!

跪拜,好文。

新注册,来顶。

这篇文章太有深度了。我完全可以说我不需要跪舔作者了。从昨天晚上看到就一直研究到今天中午,看了不下五遍。想不起来已经多少年没有看到这样的好文章了。下面是我自己的私货:

以下是我个人的一些结论,有许多有问题的地方,恳请作者指正:

1、本代ryzen的SMT对单核性能的较明显的影响是硬伤,不是可以通过优化、升级bios等可以解决的。

2、zen相对于目前kabylake/broadwell-E在指令集上的优势是SHA

3、ryzen的下一代可能会着重解决SMT的效率问题,也就是CCX的问题

4、如果ryzen的流水线是19级,那可能是amd为了能拉高频而妥协的。理论上应该能比skylake/kabylake更能超频。然而被垃圾14nm坑了(也许早就料到了所以设计的长流水线?)

此外也可以得出intel一方的一些结论:

1、skylake/kabylake并不是简单的挤牙膏。从之前我了解到的从四发射改为五发射(1复杂4简单),到现在流水线也可能增加了(haswell是14级,skl的增加是为了应对intel初期的14nm的难超频??)导致分支预测的惩罚周期增加,最终导致额外增加的1个发射数并没有理论中对性能的明显提升

2、如果按泄露的skylake XEON的L2从每核心512k增加到1M,以及AVX512的加入。如果HEDT的skylake-X使用同样的设计,相对于broadwell-E,性能会有飞跃式的提升。到今年Q3发布时应该会有好戏看了

3、intel下代的coffeelake(cannonlake?)可能会引入SHA、降低流水线长度。到时候跑分(撸大师?)可能又会有很大提升

SMT、单核性能问题已经增补跨CCX延迟测试。RYZEN的19级流水线确实弥补了GF14nm的短板,但付出了巨大的代价。在我看来第一代Zen在Core部分不过不失,而uncore部分短板明显。Intel如果后续SLX、KBLX同步登场,且在主流引入6C16T,对AMD影响巨大。

GZ上的主帖怎么不去回了?

这都预测到了。 牙膏厂8700k确实给锐龙带来了巨大冲击

单纯从理论性能上而已,RYZEN 7多线程性能要高于Kabylake,定价也仅仅是持平或者稍高。不认同这句话。

这文章我喜欢,这评论更喜欢,作者很专业的道出本真,读者没有跟风无理谩骂,很有气氛

八核到底适不适合一般人家用途,想起联发科的10核cpu了,很好玩

PC和手机不一样,手机是若干个高功耗核心+若干个低功耗核心,无法同时打开。

写的确实是好啊,在我看来除非是那帮搞龙芯的人,或者intel amd的内部人士。

amd是做的不错,大架构有牛人,但成功很在乎细节。这就是amd的弱项了,毕竟

人手不够啊

台積電的16NM還是要比samsung GF的14NM要好的

zen可以直接用服務器上面的內存么?

還是專用條?

RYZEN默认就支持ECC RAM,但不支持ECC+REG。

還記得K10各核心的異頻運作嗎,其實到FX亦沒問題,可能Ryzen可以也不一定,而且M$一直也沒有移除異頻支持

當初XP那個更新不過是注冊表補丁,所以反向而行就好

Windows Registry Editor Version 5.00

[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\Session Manager\Throttle]

“PerfEnablePackageIdle”=dword:00000000

現在你的CPU就像手機處理器般可以異頻啦

當然,因為工作量橫跨各處理器後導致閾值不達標而不作升頻又是另一回事了。

看手機處理器異頻工作、甚至大小核也沒問題,不是M$不作為的話是什麼

可能會更好超呢XD

以前工作量橫跨各處理器,或工作量在各處理器間走來走去似乎是為了降低發熱(以前的CPU沒深度睡眠什麼的),平衡CPU的老化可能也是個考量?

但現在再這麼做不過是增加功耗和發熱量。

看見什麼w7跑得比w10快,不要神化什麼调度器,可能那只是Core Parking的問題

w7的Core Parking是預設一核心開一個(實體cpu0)停一個(虛似cpu1),而w10是兩個都停掉,在注冊表PowerSettings那裏w8原本有一個隱藏的新選項可以選擇停一個定兩個一齊停掉,但w10不知道為什麼又移除掉

Core Parking是根據閾值壓制CPU核心的使用,一點也不智能,那些隱藏的閾值選項可以在注冊表PowerSettings那裏自己開來改,「壓制」和「調度」八字也扯不上吧

扒去Core Parking的外皮後即和XP的调度方式沒大區別

最好笑還有對雞血補丁的神化,M$不過將推土機當HT處理器一般的識別,將Core Parking套上去而己吧

希望M$不要再交行貨了(小修小補),認真整一個新的調度器出來,不要再戰十年

難道要等核心發展到過百才醒悟嗎

另外,这几年CPU/SoC的设计都是尽量的在功耗控制方面与系统去耦合。这主要是因为处理器并没有办法选择执行什么代码,而总是有弱智代码会请求远高于需求的资源。

Windows for IA64是重构的调度器,也是一次彻底放弃x86历史包袱的机会,然而被X64取代了。

你看到的WIndows CPU Usage其实只是图形化的表述,从core i7 4xxx开始就已经引入了粒度非常小的供电控制平面和负载控制平面。简单地说,你可以关闭所有省电功能,而在相同负载下CPU的功耗并不会显著上升。

;要在平衡計劃關Core Parking?

;在「電源選項」內打開控制Core Parking的開關吧

;Processor performance core parking min cores

;設置100%等於關閉Core Parking

Windows Registry Editor Version 5.00

[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\Power\PowerSettings\54533251-82be-4824-96c1-47b60b740d00\0cc5b647-c1df-4637-891a-dec35c318583]

“Attributes”=dword:00000000

;自主模式那麼先進的東西,可能只有SkyLake以上才支持

[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\Power\PowerSettings\54533251-82be-4824-96c1-47b60b740d00\8baa4a8a-14c6-4451-8e8b-14bdbd197537]

“Attributes”=dword:00000000

;另一個先進的東西,可能也是SkyLake以上才支持

[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\Power\PowerSettings\54533251-82be-4824-96c1-47b60b740d00\be337238-0d82-4146-a960-4f3749d470c7]

“Attributes”=dword:00000000

沒有Core Parking這個外掛根據閾值壓住CPU不給你用後,調度上其實和XP沒多少區別,只是一個喜歡將新線程從最後的CPU激活起來,一個不是,但他們的共通點就是喜歡將工作量橫跨所有CPU,完全違反近代CPU當越少內核被激活,運行頻率則越高的大原則,由Turbo Boost/推土機MAX Turbo出現到現在都好幾年啦,這就是M$在調度器設計的不作為吧。

>这样的软肋并非像昨天LISA SU电话会议宣称那样可以通过软件解决。

M$可以將兩個CCX借鑒雙路CPU的處理法,線程盡量不橫跨去另一個CCX?

每想到C6深度睡眠配合差異過大的升降頻而導致音效輸出出現的噪音…你真的要關Core Parking嗎

可谷狗c6 noise sound之類,簡直歷史由久,希望Ryzen的主板不會再有,難受。

在SMT情况下要确保线程全部处于单个CCX而不交互,难度非常大,可能需要编译器支持。

某些大大可能亂改那些隱藏設置後會想還原

例如平衡計劃的處理器設置「54533251-82be-4824-96c1-47b60b740d00」就到

HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\Power\User\PowerSchemes\381b4222-f694-41f0-9685-ff5bb260df2e\54533251-82be-4824-96c1-47b60b740d00

取得所有權和權限後將它「54533251-82be-4824-96c1-47b60b740d00」整個刪掉即可

知乎上看到过来看全文,请问作者是否能开通知乎认证号?是否允许全文转载?

简直是史诗级的文章,能否转载?比我们现在学的大学教材强太多了

不同cpu所针对的应用方向肯定不同。

纯游戏玩家高频7700k intel占优势 游戏推荐 7700k>1800x>1700x

平时喜欢一边办公,一边看看电影,一边又上着上网、一边直播等多任务进行,zen的多线程优势非常明显。

非纯游戏玩家推荐 1800x>1700x>7700k

zen的意思“禅”,zen设计初期估计也是想要各方面均衡,性能与功耗不能同时兼顾。所以zen各方面即不突出也不落后。更适用于家庭和办公使用及各类设计工作站。

敌在PR部

真的很精彩,收藏了、慢慢嚼

1800X看起来也就是3代i7 3770K的水准,多了四个核心而已

6950X看上去就像是3代3770K的水准,多了六个核心而已(滑稽

厉害了,这篇文章写得真的很好很详细,干货也很足,感觉别的网站小编都要学习一个啊!

N年前看过关于手机CPU的一片文章写的也很好,在爱活网,今天注册了个账号。

通篇看完,发现有很多错别字,希望可以修正。

今日完成了对RYZEN7处理器CCX组织的验证,本人发现RYZEN7这代是4+4架构,并且L3延迟一致性差异巨大。

AMD胶水8核被PRO-A大师揪出来一剑封喉了Orz

关于苹果收购P.A. Semi那段,特意去搜了下,是2.78亿美元。

感谢提出,已修订。

我非常赞同你对apple的ARM芯片研发的评论,apple目前的微架构设计能力不在intel之下,也许再过几个月,比Ryzen更令intel焦虑的是apple的A11。

把苹果的架构设计能力和英特尔比?呵呵。

你难道没发现Jim这帮人搞K7 K8时AMD就和intel一个水平,一旦他们离开就是AMD的推土机垃圾? 他们再次回到AMD,又是ZEN这种与intel相当的水准。 那么Jim及其师傅在AMD之外搞的项目就”大失水准”了吗? 肯定不是。2006年PA的pwrfficient就和core 2一个水平,apple Mac是计划要使用pwrfficient的,后来乔布斯转向core2,其真正原因是乔布斯想让PA陷于绝境然后吞并之, 在apple金元滋润下A系芯片都搞起人工布线。目前 A10的perf/Mhz都已经接近 x86桌面产品,不服就跑个SPEC 06看看。以apple的控制癖,将intel u请出Mac 产品线只是时间问题,PA的pwrfficient是玩了一次曲线救国而已。

pwrfficient是Core2水平?呵呵,PWF后面基本就是Apple A5,不懂别乱YY

处理器设计领域,本人最佩服Dobberpuhl和Pat Gelsinger

本人认为在这个时代讨论ISA而忽略实现是无意义的。Apple确实拥有ARM ISA阵营里最强的架构和实现。

PWRficient 的SPEC你可以去查,考虑到功耗,和core2媲美完全没问题。另外,乔布斯收购了PA等公司之后, 把cpu设计团队分成2支, 一支去搞公版cortex,A4=Cortex A8,A5=CortexA9,另一支则在A4A5应付的两年内研发出自主微架构A6,乃至A7A8A9A10,这自主微架构的ARM才是这帮人的真实水平,说白了,intel的atom/coreM在移动领域算是遇到StrongARM 2.0了,intel力不能支啊。

从Cyclone(A7),Apple就已经有业界Top 5的CPU架构和设计团队了。Dobberpuhl也是在此时退休的。

照你这么说三星猎户座准备也要吊炸天了呢

安卓阵营ARM的IPC只有A10的一半左右,你开什么玩笑。

猎户座也有设计?不是1:1的ARM标准实现吗?楼主真的懂?

今天看国内外媒体都说Ryzen有19级流水线,点引用发现都是这篇文章。能否给出更多验证过程?

分支预测失败惩罚循环测试中已经有充足数据验证。

深度好文章!感谢作者这么用心!

跪着读完

看完这篇文章,注册个账号

通篇读完觉得作者的评价还是具有一些主观的痕迹,您对产品的技术方案选用和销售策略的推定我看不大懂,里边似乎有一些前后矛盾的地方,比如不用“钎焊“是因为自信,而用了是“勤能补拙“,这个说法让我有些不明就里。另外关于反垄断法案,可能我和您的理解有一些偏差,我不认为intel作为技术企业会因为技术上的领先导致该方面的法务纠纷。抛开测试数据,不少评价文字让人觉得:恰恰是amd带来的压力成为了Intel继续成功的条件,因而大家应该对intel当前和今后的产品更有信心,比如降价的7700k和日后不知什么型号的i357。。。我觉得把数据摆上就够了,评价的事交给读者自己去做就好。作为一名从事相关专业多年的工作者同时也是一名普通消费者的一点个人看法。

用硅脂封装还是钎焊主要建立在Intel 14 vs GF14基础上。本人认为GF14不适合用来生产高性能桌面处理器。AMD被迫使用GF14后已经把1800X性能推向了工艺极限。

补充:首发产品就逼近工艺极限,对任何半导体来说都不是好事。

下一代ZEN+应该还会有工艺改进吧?

另外那些12nm 4nm都是些什么鬼

确实,首发就推到工艺极限确实不是好事,例如黄老板的呆瓜处理器。本来是坑的高通骁龙不要不要的。结果一下子自己坑死了。变成平板CPU

前排围观神文

炮村的顾大师消失之后,很少能有媒体能达到这样的深度。

顾X这种是就比提了,YY成分比较高 ,时常写出来批判amd一番搞得自己要比厂商牛逼一样,各种私底下各种讽刺amd怀着偏见写出来的的东西就吧amd说得一文不值,去看看当年他写的7970各种表达对amd失望,设计各种不合理,现在不是打脸了吗

看了两年爱活 看到这篇文章特意注册个账号支持一下

别人都能看懂的文章。。我看不懂。。。

炸裂

为啥温度这么高

本人认为GF14nm并不是制造高频率桌面处理器的最佳选择。

特意注册一个帐号,回复一下。

目前中文最好评测。

写的好! 求更多

很久没看到这种好文了,确实不错!

这哪是AMD翻身,分明是爱活评测翻身了

爱活评测本来就很有水准,高通塞钱之前的手机cpu评测简直是所有网站里最详细的。

evolife原本就是3C业界的dalao们搞出来的,很多作者都是从上个世纪写到现在。

翻身了!!!!

目测爱活硬起来 硬起来

大神啊,我一个字一个字,读完了。精品评测文,比超能写的好太多了,那些大炮村、大炮洋,我是一目一段,蛆家评测一目十行,写的什么玩意儿!AMD Ryzen评测这篇是最深入的,国外的Anandtech网站都望其项背啊!神,大神啊!

好文章,学习了~

服了,其中还有好多看不懂

跪着看完了,服

贴吧过来都看哭了

作为混卡巴的小白表示这篇文章真的很强很详细有些根本看不懂。。

PRO-A是哪位大神编辑?竟能写入如此深度好文 有当年《微型计算机》的感觉

微机不就是intel御用枪手么

PRO-A是哪位大神编辑?竟能写入如此深度好文 有当年《微型计算机》的感觉

感觉亚洲也就后藤弘茂能比了

後藤なんか、Pro-A先生に比べるもんじゃないよ

扛鼎

难得的好文章,学习了

用测试把amd不想说的故意模糊的全部验证出来大写服

这文章缺少了编译器性能测试,还有就是specint测试,这两样是最体现理论性能的

农企岂不是要脸着地?

SPEC里面RYZEN的成绩很难看。但这主要原因可能是编译器。

phoronix 和 openbenchmarking 上有编译 linux 内核的测试,编译器参数都很全。

Ryzen需要Linux Kernel 4.9.10以上才能正常使用。现在还没有合适的开源编译器脚本进行测试。

phoronix 测试用的貌似是 ubuntu 自己编译好的 4.10.0-9-generic,gcc 有 -march=znver1 参数优化。

谢谢提出,稍后测试。

AMD貌似有了自己的GCC编译器?

手机上看坐过站了。。。精彩

真比那些什么小编高不知道哪里去了

2ch上居然有这篇文章的日文编译,日本人只编译了一半不过瘾,来看下全文

量大 没那么快

求个日文版传送门

Superpi测的是整数性能,全文很好,但犯这种低级错误只能说白璧微瑕。

别闹,确实有一些笔误但是Super PI测试的是浮点没错

SuperPi主要考察处理器的浮点性能。

太可怕了,是爱活么?感觉今天正面刚了其他站

目测爱活硬起来各类it门户都得跪

希望有一大波软件支持zen后的重新测试

看了半天,最后几段才是作者想说的。这么多线程日常是没用的,单线程性能好才是最有用的。intel构架的单线程比RYZEN好。。。同理就是要买intel的才是最佳的选择的。我也只能呵呵了

那么长的文章,我居然在手机上看完了,太精彩了

写的太好了,感谢

屏蔽线程测试。。。有误导。。。感觉整个测试就是向着iu有利的方面做。。

同感,amd真正优势在多线程

Zen的L3存在较大问题,多线程也不会有优势。

虽然长,但是全是干货没一句废话

小编,文中的Ryzen 4核 是屏蔽一组CCX而来的吧?

不是,AMD的8C和4C是两种不同的DIE,这是出于成本考虑的

高通GPU是ATI的 纳尼

这的确是真事,不然高通哪来这么给力的GPU?

从Adreno 300开始高通基本完全改掉了Imageon的架构,现在的更接近PowerVR

感觉是AMD中出了个叛徒

“AMD是说到做到的公司。” ——AMD时任CEO Rory Read 笑死我了

pro-a丢了黑人问号过来hhhhhhhh

一项集体诉讼已经把芯片制造商AMD公司告上加州法院,这项诉讼原告声称AMD涉嫌欺骗消费者,通过夸大推土机核心数量,误导消费者购买其推土机处理器。

当年判决是AMD赢

这样抖包袱晒资深有意思么?10年前Pro-A就被扒皮是AMD Austin的

Austin不就是设计了垃圾推土机么?呵呵,这也好意思叫大师?

proa丢了黑人问号过来hhhhhhhh

真恶心,捧杀AMD有意思么?

没有意思么?

看了其他网站的文章,确实和这个相比天渊之别

CTO叫Papermaster,这真的不是恶搞么?

AMD现任CTO确实是叫Mark Papermaster

太猛了,很多内容第一次看到,作者是AMD工作了很多年的吧?

原来AMD也要给GF分手费的,哈哈哈哈哈哈哈

这篇文章是否可以转载?

那个工艺对比……台漏电,哈哈哈哈哈

无论如何,AMD还是赢了,价格便宜,性能更强,这个结论并没有变化。

又一个没看懂就单方面宣布胜利的

赢在哪?哪里能看出AMD赢了?

贴吧观光团特来观摩

大炮村之流看上去就像是小学生写的作文,DIY后继无人了啊

同感,估计才刚学会跑分

太可怕了,这是直接扒皮裸奔

垃圾评测,活该你们用一辈子1万多的CPU

fx57用户表示这U可用一辈子.手动滑稽

震撼……

太牛了,看了那么多网站的Ryzen评测,只有这篇没用AMD的官方文档

终于看完了,AMD的功耗是虚标的啊?L3为啥那么慢?

这个问题已经验证完成写入本文内,AMD跨CCX之间连接的有巨大延迟。

博弈啊,AMD的HEDT平台胶水一下就可以了···

Pro-A憋了十年的毒奶助力农企成功360度翻身????

这位大牛以前在哪里发文章?10年前我还是小学生……

ATI没死GZEASY还健在的年代

原来PRO-A大师去了宁美国度!

原来农企假翻身

PRO-A大师,555555

PRO-A重现江湖

这是完全把RYZEN扒皮啊,AMD杀手已经上路

别人会写的内容,我不写。别人跑过的测试,我不跑。别人写透写明白的内容,我不写。太牛了

AMD要发律师函了

PRO-A大师,哭了……10年没出来了

爱活后台很硬啊